# A More Precise Abstract Domain for Multi-level Caches for Tighter WCET Analysis

Tyler Sondag and Hridesh Rajan

Dept. of Computer Science

Iowa State University

Ames, IA 50011

{sondag,hridesh}@iastate.edu

Abstract— As demand for computational power of embedded applications has increased, their architectures have become more complex. One result of this increased complexity are realtime embedded systems with set-associative multi-level caches. Multi-level caches complicate the process of program analysis techniques such as worst case execution time (WCET). To address this need we have developed a sound cache behavior analysis that handles multi-level instruction and data caches. Our technique relies on a new abstraction, live caches, which models relationships between cache levels to improve accuracy. Our analysis improves upon previous multi-level cache analysis in three ways. First, it handles write-back, a common feature of cache models, soundly. Second, it handles both instruction and data cache hierarchies, and third, it improves precision of cache analysis. For standard WCET benchmarks and a multi-level cache configuration analyzed by previous work, we observed that live caches improve WCET precision resulting in an average of 6.3% reduction in computed WCET.

#### I. Introduction

Computing an upper bound on execution time, known as worst-case execution time (WCET), for programs running on real-time systems with hard deadlines is crucial [1]–[3]. It is essential that the computed upper bound must be sound (longer than any possible execution) [1]. However, an upper bound that is too high will result in wasted resources [1]. This is a difficult problem that requires determining upper bounds on program paths, memory access times, etc [1].

One aspect of this problem is determining an upper bound on each memory access. To drastically reduce memory access time, many processors incorporate caches, some with multiple levels. Other cache optimizations include splitting instruction and data caches. Due to the complexity of caches (multiple levels, shared vs. unified levels, associativity, replacement policy, etc), analyzing the behavior of these caches is difficult. However, if we can analyze the cache behavior precisely, we can dramatically reduce the computed worst case access time for memory accesses [2].

A large body of previous work exists to analyze cache behavior statically [1]. However, these techniques either focus on instruction caches [2], [4]–[8], or only handle single-level data caches [9]–[12]. Thus, they do not support systems that incorporate both instruction and data caches. Furthermore, since they only treat single-level data caches, they do not handle *write-back*. Write-back is a common

technique used in data caches to reduce memory accesses when contents in a cache are modified. With write-back, when a modified content is evicted from cache, it is written to the next cache level or memory. So, the next access to this content may be a cache hit, whereas previous work would sometimes classify it as a potential cache miss. This affects the upper bound on memory access time. We also show that if existing analyses are applied to unified (instruction+data) cache hierarchies with write-back the result is unsound.

Our contribution is an analysis for multi-level instruction and data cache hierarchies. There are two main novelties of our technique. First, we consider the cache hierarchy as a whole (as opposed to analyzing cache levels in the hierarchy separately [4]–[12]), which improves precision. Second and more importantly we add a new abstraction, *live caches*, to the classical abstract domain for caches [2] to handle multi-level caches. Live caches describes relations between pairs of cache levels (in order to reduce the imprecision of the join analysis [2], [4]) as well as information inside a cache level (in order to handle write-back).

Improving precision is important because a misclassified memory access may drastically increase computed upper bounds of the WCET analysis, e.g. a cache miss may be as much as 30x more expensive compared to a cache hit [13]. Soundness of cache analysis is important because it directly affects soundness of WCET. An unsound application of a cache analysis may lead to incorrect WCET.

Similar to previous work [2], [9], we have used the WCET benchmarks maintained by the Mälardalen WCET research group [14] to evaluate our technique. For 20 out of 32 (62.5%) of these benchmarks our analysis technique showed precision improvements over previous analysis. On an average we saw a 6.3% reduction in computed WCET as a result of our multi-level cache analysis technique. This result is significant because it directly translates to a corresponding reduction in wasted resources for real-time systems [1].

In the rest of this paper, we discuss the technical underpinnings of this work that include:

- the definition of live caches and illustration of the key aspects of their behavior,

- an abstract interpretation for multi-level instruction and data cache analysis, and

- an empirical evaluation of our cache analysis.

```

1 A input(*sum)

2 A if(!*sum)//init arr

3 A for(i=0; i<10; i++)

4 A arr[i] = 0;

5 B else //compute sum

6 B for(i=0; i<10; i++)

7 B *sum += arr[i];

8 B output(*sum);</pre>

```

| Variable | Cache block |

|----------|-------------|

| sum      | x           |

| arr[0-7] | y           |

| arr[8-9] | z           |

| i        | register    |

| State                 | Line #                     | Concrete states                               | Abstract hit state | Abstract miss state                              |

|-----------------------|----------------------------|-----------------------------------------------|--------------------|--------------------------------------------------|

| $S_1$                 | After 2                    | Inst   Data     L1   A                        | same as concrete   | same as concrete                                 |

| $S_2$                 | After first execution of 4 | L1 A y x<br>L2 y x A                          | same as concrete   | same as concrete                                 |

| $S_3$                 | After 4                    | L1 A Z Y<br>L2 Z Y X A                        | same as concrete   | same as concrete                                 |

| $S_4$                 | After first execution of 7 | L1 B A X Y<br>L2 Y B X A                      | same as concrete   | same as concrete                                 |

| $S_5$                 | After 7                    | L1 B A X Z<br>L2 Z y B X                      | same as concrete   | same as concrete                                 |

| $S_6$                 | Before 8                   | L1 A                                          | L1 A Z<br>L2 Z Y X | L1 <i>B,A</i>   <i>x,z y</i> L2 <i>z y B,x A</i> |

| <i>S</i> <sub>7</sub> | After instruction fetch 8  | L1 B A Z y OF B A X Z<br>L2 B Z y X Z Z y B X | L1 B Z Z L2 L2 Z y | L1 B A x,z y<br>L2 z y B,x A                     |

| $S_8$                 | After 8                    | L1 B A X Z OF B A X Z<br>L2 X B Z Y Z Y B X   | L1 <i>B</i>        | L1 B A X Z<br>L2 Z Y B,x A                       |

Figure 1. Left: code example. Letters after line numbers indicate instruction cache block containing the code for the line. Table shows variable to cache block mapping. Right: cache contents for each state using previous analysis [2]. Bold cells denote data cache. Loop unrolling is assumed.

### II. PROBLEMS WITH EXISTING CACHE ANALYSES

We first describe a typical cache analysis using abstract interpretation [2]. Basic cache terms are as follows.

- Lx "cache level x". Lower levels are closer to the processor and faster, but smaller.

- $capacity_x$  denotes the size in bytes of the Lx cache.

- line  $size_x$  (block size) is the number of bytes loaded into the Lx cache upon a miss.

- *Block* refers to a segment of memory. As viewed from the Lx cache, there are  $\mathcal{M}/line\ size_x$  blocks of memory, where  $\mathcal{M}$  is the capacity of memory.

- Associativity is the number of cache lines a memory block may reside. In a 2-way associative cache, a block may be in one of two cache lines. A 1-way associative cache is direct mapped and capacity, line size, way is fully associative.

- Hit/Miss When a memory location is in a cache level, it is a hit; otherwise, a miss.

- Replacement strategy: A technique to determine which block to replace when a cache is full and an additional block is needed. Like [2], [4], we use the least recently used (LRU) policy where the block accessed least recently is removed, however, other policies could also be used.

- *Mainly-inclusive*: The relationship between cache levels. In this policy, cache levels operate independently. Updates for higher cache levels are determined based on misses and write-backs from the previous level. If Lx and Lx+1 are mainly-inclusive, then most blocks in Lx are also in Lx+1.

### A. Abstract Interpretation based Cache Analysis

Figure 1 illustrates an abstract interpretation of cache behavior for a two level cache hierarchy. The first level, L1, is a split (instruction separate from data) 2-way associative cache. The second level, L2, is a unified (containing both instruction and data blocks) 4-way associative cache. Both levels use LRU as a replacement policy with write-back and have a line size of 32 bytes. For simplicity, we consider one cache set from each cache. Since the concern is cache hits and misses, the cache state aims to capture when blocks are loaded into and evicted from each cache level.

The left side of the figure shows sample code. Letters after line numbers indicate the instruction cache block the code belongs to. The right side illustrates states for the cache analysis (assuming the initial state is empty). The column marked with concrete states shows the cache states according to the concrete semantics, whereas those marked with abstract show the states of the cache from the point of view of abstract hit/miss analysis. Thus imprecision in analysis can be analyzed by comparing them.

Similar to previous work [2], [4], for each point in a program, assume there is a list of reads and writes to analyze. Based on the reads and writes for a program point, the state of the cache is updated. Since existing cache analysis techniques [2], [4] do not handle write-back, in this example there is no difference between reads and writes.

After analyzing lines 1–2, state  $S_1$  results. L1 shows instruction cache block A as the most recently used instruction cache block and x as the most recently used data cache block. L2 shows that x was the most recently accessed block. Notice that since L1 is a split cache instruction and data blocks are treated separately, whereas since L2 is a unified cache both type of blocks are treated uniformly.

Depending on how the **if** condition on line 2 evaluates control might be transferred to either line 3 or line 6. Both paths must be analyzed because actual path is unknown.

Let us first analyze the loop on lines 3–4. Note that variable i is assigned to a register and does not impact the data cache behavior. For simplicity we assume that the loop has been completely unrolled.  $S_2$  shows the state after analyzing the first loop iteration. Assume that the first 8 locations of array arr are in block y and sizeof(int) is 4.  $S_2$  shows that block y is the most recently accessed block in L1 data cache and most recently accessed block in L2. Tracking actual values for variables is not necessary as it doesn't influence the hit/miss behavior [4].  $S_3$  shows that state after all executions of the loop, where L1 data cache contains the entire array arr (both blocks y and z).

Next, we analyze the loop on lines 6–7. Note that the state  $S_4$  corresponding to this code is derived from  $S_1$

not  $S_3$ . On line 7, the value in  $\mathtt{arr[i]}$  is fetched first followed by adding the result to  $\mathtt{sum}$ . Thus, after the first iteration  $S_4$  shows us that x is the most recently used block in L1 data cache, but block y has been loaded into both levels. Further, before these data locations were referenced, instruction block B was loaded into L1 instruction cache and L2. State  $S_5$  results after analyzing all iterations of the loop.  $S_5$  is similar to  $S_4$  but block z has also been loaded into both cache levels.

**Join function:** When line 8 is analyzed, there are two predecessor lines 4 and 7 with state  $S_3$  and  $S_5$  respectively. Thus, the analysis must merge or "join" the states denoted as  $S_6 = S_3 \bigwedge S_5$ . Figure 1 shows the merged states for a "hit" and a "miss" analysis. The hit analysis tells us for each reference "hit" or "unknown" and the miss analysis tells us "miss" or "unknown". For example, if a block is in a state of the hit analysis, it must be a hit, otherwise it is unknown.

For the "hit" state, the worst case of block locations is used. For example, the L1 instruction cache block A was in the last space in  $S_5$  and the first space in  $S_3$ . Thus, A in  $S_6$  takes the last position in the L1 instruction cache.

For the "miss" state, the best case is chosen. For example, block B is in the first position of L1 in  $S_5$  but is not in L1 cache in  $S_3$ . Thus in  $S_6$ , B takes the first position in the L1 instruction cache.

After merging potential states, line 8 is analyzed. First, instruction block B is fetched giving state  $S_7$ . Since B is not in hit analysis state  $S_6$ , B is added to L1 updating the LRU order and evicting A. We can see by looking at the possible concrete states that B may actually be an L1 hit meaning it is not sound to update L2 with B. The analysis does not have the luxury of considering all possible concrete states. In general, thus the analysis uses the miss analysis and only updates L2 with the block if the miss analysis can guarantee the reference will miss L1. Otherwise, an update to L2 with an empty block is done. Therefore, in this example, B is not added to L2 since the miss analysis can not guarantee that B will miss L1. However, the LRU order of L2 must be updated in case B does miss so an empty block is used.

Next, block x is accessed resulting in an update to L1 data cache as shown in  $S_8$ .

### B. Problems that Affect Soundness and Precision

With the background on abstract interpretation based cache analysis in place, we now illustrate the three problems with existing techniques via our example in Figure 1.

**Cache hierarchy:** Consider the position of instruction block A in L1 of state  $S_1$  of Figure 1. Even though A is the most recently used block in the L1 instruction cache, x is the most recently used block in L2. This position of A in L2 shows how data cache behavior affects the behavior of instruction blocks in a unified L2 cache. Since most L2 caches are unified, simultaneously analyzing both instruction and data behavior is necessary.

**Write-back**: Since analyzing both instruction and data cache is required, handling write-back properly is essential. To illustrate the need to handle write-back, let us revisit the transition from  $S_7$  to  $S_8$  of the hit analysis in Figure 1. In the "hit" state for  $S_7$ , block z in L1 may be dirty. In the transition to state  $S_8$  this block is evicted. As a result of the potential eviction of a possibly dirty block, L2 should be updated. This additional update would force block y out of L2. Without considering write-back, the analysis would report that y must hit L2 which is not sound. For unified cache levels write-back also affect the soundness of instruction caches since data cache write-backs to L2 impact the instruction cache blocks in L2. Thus, it is crucial to handle write-back properly in a multi-level cache analysis.

**Precision:** Notice the existence of block x in both potential concrete states of  $S_7$  in Figure 1. This means that x must be somewhere in the cache, however, the hit analysis can not guarantee this. Thus, even though the reference to x on line 8 will be a "hit", the analysis says "unknown" or worst case memory access. This loss of information is due to the sound approximations of the join function. Since joins are frequent (**if**s, loops, etc), the precision of the join function is key to the overall precision of the analysis.

### III. MULTI-LEVEL CACHE ANALYSIS WITH LIVE CACHES

The soundness and precision problems with existing analyses arise because they do not take into account the global view of the hierarchy. As a result, they miss the cache blocks that must exist in the hierarchy, even though their existence in any cache level may not be soundly computed. They also do not soundly capture write-back. To solve these problems we introduce a new abstraction to the classic abstract domain of caches, that we call *live caches*.

### A. Live Caches

A live cache is an abstract cache maintained for the purposes of multi-level cache analysis. For every pair of concrete cache levels the analysis maintains one live cache. These live caches contain blocks that must exist (blocks that are live references, thus the term live caches) in at least one of two different cache levels. The example in Figure 1 contains two cache levels L1 and L2. Thus the multi-level cache analysis maintains one live cache  $\bar{C}_{1\leftrightarrow 2}$ .

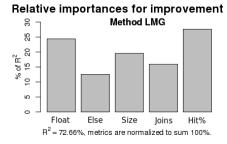

Figure 2 shows the "hit" analysis state for  $S_1$  from Figure 1 as determined by our analysis. This state now includes the live cache  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$ . The state for L1, L2, and  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$  is shown on top-left, bottom-left, and bottom-right respectively in this section. The live cache  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$  consists of two sets, one corresponding to L1 instruction cache and L2 and the other corresponding to L1 data cache and L2.

The associativity of each set in the live cache is equal to the larger of the two caches, e.g. the associativity of  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$  is 4 since that is the larger between L1 and L2.

Figure 2. Hit analysis state for  $S_1$  Figure 3. Hit analysis state for  $S_2$

The position of a block in live cache is determined by taking the better case of the same block's position in the two cache levels that the live cache relates. This is because a live cache is updated whenever either of its corresponding cache levels, more specifically sets, is updated.

As mentioned previously, write-back introduces new behavior that must be modeled. Consider an example for the "hit" analysis for  $S_2$  in Figure 3. The y' notation in L1 of  $S_2$  means that the block y is dirty (modified).

To handle the addition of live caches and write-back, the join functions for both the "hit" and "miss" analysis must be modified. For the "hit" analysis, when a block exists in both states, the resulting block is dirty only if both blocks are dirty. However, in the case that only one block is dirty, we must keep track that a potentially dirty block may exist in that cache location in order to safely handle write-back. For live caches, we join the two corresponding cache levels giving blocks the worst-case proximity to eviction between the two. For the "miss" analysis, when a block exists in both states, if either block is dirty, the resulting block is dirty.

Figure 4. Hit analysis state for  $S_6$  from Figure 1

Consider the join of states  $S_3$  and  $S_5$  to create  $S_6$  for the "hit" analysis in Figure 4. Locations of blocks in live cache are determined similar to the previous examples except for block x. The location for x is chosen as a worst case location between x in L1 in  $S_5$  and L2 in  $S_3$ . Also, note that in  $S_5$ , z is clean in L1 but in  $S_3$  it is dirty. Thus, in  $S_6$ , z'' denotes that z may be dirty in L1. Also, notice that in  $S_3$ , y exists in L1 and is dirty, however, y does not exist in L1 in  $S_5$ . Thus, since we can not guarantee y will be in L1 cache, y should not exist in L1 in  $S_6$ . However, since y may exist and may be dirty, when it may be evicted from L1, the LRU order of L2 should be updated. Thus, y should not be reported as a hit if accessed (denoted by y) but is kept in the state so higher levels can be modeled in a sound way. Even though y is modeled in the "miss" state, we can not safely use eviction from L1 in the "miss" state to update L2 because of the difference in updates for the "miss" analysis.

Consider the same join for the "miss" analysis. Even though z is clean in L1 of  $S_5$ , since it is dirty in L1 of  $S_3$ , it is dirty in L1 of  $S_6$  for the "miss" analysis.

Finally, we must consider how live caches are updated. Recall that a live cache must be updated whenever either of its corresponding levels, more specifically sets, is updated. To avoid duplicate updates, we only need to update a live cache once if both corresponding sets are updated as a result of the same memory access. For example, Figures 5 shows states  $S_7$  and  $S_8$  from Figure 1 extended with live caches.

Figure 5. Hit analysis states for  $S_7$  and  $S_8$  from Figure 1

Recall that the transition from  $S_6$  to  $S_7$  in Figure 1 involved an update of both L1 instruction cache and L2 cache. Thus, the corresponding live cache sets in  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$  must also be updated. Here, upon reading block B, both sets in  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$  are updated. This results in eviction of block A and block x being moved to the last position in  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$ .

#### B. Benefits of Live Caches

Live caches have several benefits in that they help address the problems described in Section II-B. We now describe each of these benefits.

Improved precision: Recall in the example from Figure 1 that when reading x on line 8, the hit analysis could not guarantee a hit even though x is in both concrete states in  $S_7$ . In Figure 4, block x was in the second last position in the L1 data cache of  $S_5$  and in the second last position in the L2 cache of  $S_3$ . Thus, in the resulting state,  $S_6$ , x took the second to last position (worst case) in the live cache  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$ . Now, consider the read to x again but using the state  $S_7$  augmented with live caches from Figure 5. Since x is in the live cache  $\bar{\mathcal{C}}_{1\leftrightarrow 2}$ , we know that in the worst case, xwill hit L2. Thus, by adding live caches, an unknown, or worst case memory access, has been classified as a worst case L2 hit. For this example, we see that introducing live caches results in an access being classified as a hit of some cache level rather than a worst case memory access. Thus, live caches improve the overall precision of the analysis.

**Write-back**: To illustrate how these changes ensure soundness for the "hit" analysis, consider the transition from state  $S_7$  to  $S_8$  in Figure 5 as compared to the previous example in Figure 1. In the transition in Figure 5, two potentially dirty blocks are evicted from L1 (z and y). Thus, L2 cache must be updated once for potential write-back (since loading in one new block can not result in two write-backs). Further, we update L2 again for the potential L1 miss of block x. Again we can not update L2 with x since the miss analysis can not guarantee L1 miss.

**Hierarchy**: As discussed previously, a sound analysis must model both instruction and data caches due to their impact on each other in unified cache levels. Thus, our analysis simultaneously analyzes both cache types. Also, the hierarchy as a whole contains more information than the levels do in isolation. Thus, our analysis introduces live caches which capture additional information available from the hierarchy as shown in Figures 4 and 5 with block x.

We now define the theory of our multi-level cache analysis. As is usual for an abstract interpretation based analysis [4], we first define the concrete behavior for a common type of cache hierarchy (Section IV). Then (Section V) we define the abstraction of the concrete behavior for multi-level caches and the formalism behind live caches.

#### IV. CONCRETE CACHE SEMANTICS

In this section, we define the concrete semantics for caches. That is, their *observable behavior*, not their physical behavior. Here, we focus on mainly-inclusive caches, a common multi-level cache policy (Pentium II, III, 4, etc). The discussion for other types of cache hierarchies is contained in our report [15]. Figure 6 shows our notation for concrete semantics. It is inspired from Ferdinand and Wilhelm [3], but extends it to multi-level caches.

| $n_x$ :                                                                                                                                                                                                                                                                                                       | The <b>number of blocks</b> that fit into the Lx cache at one time. $n_x =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                               | $capacity_x/line\ size_x.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $A_x$ :                                                                                                                                                                                                                                                                                                       | <b>Associativity</b> of the Lx cache $(A_x$ -way set associative). For direct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                               | mapped caches, $A_x = 1$ and for fully associative, $A_x = n_x$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| H:                                                                                                                                                                                                                                                                                                            | $H = \langle C_1, \cdots, C_N \rangle$ , where N is the number of cache levels. State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                               | of the cache hierarchy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $C_x$ :                                                                                                                                                                                                                                                                                                       | $C_x = (S_{1,x}, \dots, S_{n_x/A_x,x})$ The $x^{th}$ level of cache (L1, L2, etc) and consists of $n_x/A_x$ cache line sets (or block sets).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $S_{i,x}$ :                                                                                                                                                                                                                                                                                                   | $S_{i,x} = \langle l_{1,x}^i, \cdots, l_{A_x,x}^i \rangle$ Represents an associative cache set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -,                                                                                                                                                                                                                                                                                                            | Sequence of cache lines, ordering defines the LRU order where the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                               | last line is the least recently used. $S_{i,x}(l_{j,x}^i)$ is a look-up of the block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                               | in the $j^{th}$ line in the $i^{th}$ cache set of the Lx cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $l_{j,x}^i$ :                                                                                                                                                                                                                                                                                                 | The $j^{th}$ cache line in the $i^{th}$ associative set in the Lx cache (contains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| J, x                                                                                                                                                                                                                                                                                                          | one memory block).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $M_x$ :                                                                                                                                                                                                                                                                                                       | Set of blocks $\{m_{1,x}, \cdots, m_{\mathcal{M}/line\ size_x,x}\}$ , where $\mathcal{M}$ is the capac-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                               | ity of memory. $M_x$ models the memory as viewed from the Lx cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                               | The line size changes this view of memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $m_{i,x}$ :                                                                                                                                                                                                                                                                                                   | The $i^{th}$ memory block as viewed from the Lx cache (as large as the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                               | line size of $Lx$ cache).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I:                                                                                                                                                                                                                                                                                                            | empty block indicates that no value exists in cache yet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $M'_x$ :                                                                                                                                                                                                                                                                                                      | $M_x' = M_x \cup \{I\}$ memory with the empty block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                               | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x : M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $M'_x$ :                                                                                                                                                                                                                                                                                                      | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x: M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $M_x'$ : $adr_x$ :                                                                                                                                                                                                                                                                                            | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x: M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(line\ size_x) \rfloor$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $M'_x$ :                                                                                                                                                                                                                                                                                                      | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x: M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(\text{line } \text{size}_x) \rfloor$ . $set_x: M_x \to C_x$ maps blocks to cache sets. $set_x(m_{i,x}) = S_{j,x}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $M'_x$ : $adr_x$ : $set_x$ :                                                                                                                                                                                                                                                                                  | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x : M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(line\ size_x) \rfloor$ . $set_x : M_x \to C_x$ maps blocks to cache sets. $set_x(m_{i,x}) = S_{j,x}$ , where $j = adr_x(m_{i,x}) \mod (n_x/A_x) + 1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $M_x'$ : $adr_x$ : $set_x$ : $\delta$ :                                                                                                                                                                                                                                                                       | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x : M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(line\ size_x) \rfloor$ . $set_x : M_x \to C_x$ maps blocks to cache sets. $set_x(m_{i,x}) = S_{j,x}$ , where $j = adr_x(m_{i,x}) \mod (n_x/A_x) + 1$ . $\delta : C_x \times S_{i,x} \to \{true, false\}$ True if the input block is dirty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $M'_x$ : $adr_x$ : $set_x$ :                                                                                                                                                                                                                                                                                  | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x: M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(line\ size_x) \rfloor$ . $set_x: M_x \to C_x$ maps blocks to cache sets. $set_x(m_{i,x}) = S_{j,x}$ , where $j = adr_x(m_{i,x}) \mod (n_x/A_x) + 1$ . $\delta: C_x \times S_{i,x} \to \{true,false\}$ True if the input block is dirty. Used for cache levels with different line sizes. e.g.: $m_{i,x} \preceq m_{i',x+1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $M_x'$ : $adr_x$ : $set_x$ : $\delta$ :                                                                                                                                                                                                                                                                       | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x: M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from Lx cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(line\ size_x) \rfloor$ . $set_x: M_x \to C_x$ maps blocks to cache sets. $set_x(m_{i,x}) = S_{j,x}$ , where $j = adr_x(m_{i,x}) \mod (n_x/A_x) + 1$ . $\delta: C_x \times S_{i,x} \to \{true, false\}$ True if the input block is dirty. Used for cache levels with different line sizes. e.g.: $m_{i,x} \preceq m_{i',x+1}$ means that all of $m_{i,x}$ is in $m_{i',x+1}$ Formally, $m_{i,x} \preceq m_{j,y} \Leftrightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

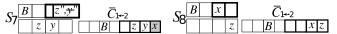

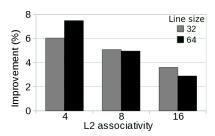

| $M'_x$ : $adr_x$ : $set_x$ : $\delta$ : $\preceq$ :                                                                                                                                                                                                                                                           | $M_x = M_x \cup \{I\}$ memory with the empty block. $adr_x : M_x \to \mathbb{N}$ function mapping memory blocks (as viewed from $Lx$ cache) to their start address and is defined as $adr_x(m_{i,x}) = n$ where $n = \lfloor i(line\ size_x) \rfloor$ . $set_x : M_x \to C_x$ maps blocks to cache sets. $set_x(m_{i,x}) = S_{j,x}$ , where $j = adr_x(m_{i,x}) \mod (n_x/A_x) + 1$ . $\delta : C_x \times S_{i,x} \to \{true, false\}$ True if the input block is <b>dirty</b> . Used for cache levels with different line sizes. e.g.: $m_{i,x} \preceq m_{i',x+1}$ means that all of $m_{i,x}$ is in $m_{i',x+1}$ Formally, $m_{i,x} \preceq m_{j',x+1}$ ad $r_y(m_{j,y}) \le adr_x(m_{i,x}) \le adr_y(m_{j+1,y})$ , $x < y$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |